在光通信技术高速发展的今天,光电器件的封装形式正经历着一场深刻的变革。从早期标准化的可插拔模块,到如今前沿的光电共封装(CPO)技术,这一演进不仅反映了系统对带宽、密度和能效的极致追求,也揭示了光电子与硅基集成电路深度融合的未来趋势。

第一阶段:可插拔模块的黄金时代

可插拔光模块(如SFP、QSFP系列)的出现是光通信走向标准化和商业化的里程碑。它将激光器、探测器、驱动电路等封装成一个独立、热插拔的“黑盒”,通过标准电接口(如SerDes)与交换机、路由器的主板连接。这种设计带来了无与伦比的灵活性、互操作性和易于维护的优势,支撑了数据中心和电信网络过去二十年的爆炸式增长。随着数据速率向400G、800G乃至1.6T迈进,可插拔模块的物理尺寸、功耗和面板前端I/O密度逐渐触及瓶颈。高速电信号在PCB板上的传输损耗和串扰日益严重,成为提升系统整体性能和能效的桎梏。

过渡阶段:板上光学与近封装光学

为了突破可插拔模块的限制,产业界探索了中间路径,如板上光学(On-Board Optics, OBO)或近封装光学(Near-Package Optics, NPO)。这些技术将光学引擎从面板前端移至主板之上,更靠近交换芯片,从而缩短了高速电通道的长度,降低了传输损耗和功耗。光引擎与电芯片仍通过PCB互连,并未实现根本性的集成,在进一步提升带宽密度和能效方面仍有局限。

新纪元:光电共封装技术的崛起

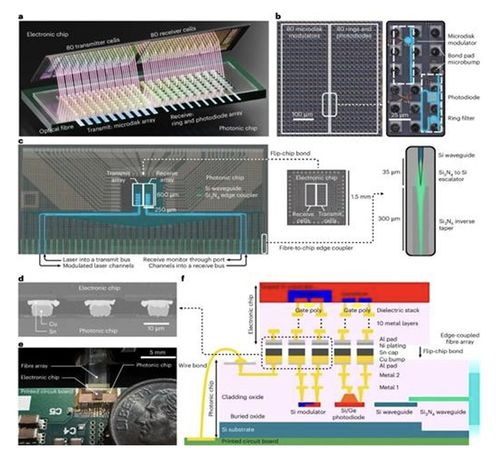

光电共封装技术代表了当前演进的前沿方向。CPO的核心思想是将硅光芯片或III-V族光引擎与高速计算芯片(如交换机ASIC、GPU、CPU)通过先进的封装技术(如硅中介层、再布线层)集成在同一个基板或封装内。它们之间的互连从PCB板级提升到封装内部,实现了超短距、超高密度、低损耗的互连。

CPO技术带来了革命性的优势:

- 极致能效:大幅缩短了电互连距离,将SerDes的功耗从可插拔方案中的数瓦降低到几乎可以忽略的水平,系统总能效显著提升。

- 超高带宽密度:突破了前面板插拔空间的物理限制,使得单位面积能够实现Tb/s量级的I/O带宽。

- 更优的信号完整性:封装内超短互连极大降低了信号衰减、反射和串扰,支持更高速率的调制格式。

- 系统简化与成本潜力:减少了外部组件数量,简化了系统设计,长期看有助于降低单位比特成本。

挑战与未来展望

尽管前景广阔,CPO技术的全面商业化仍面临散热管理、封装工艺复杂性、标准化、可维护性与供应链重构等多重挑战。特别是如何平衡高性能集成与必要的可维修性,是亟待解决的工程难题。目前,CPO正率先在超大规模数据中心内部、人工智能集群等对带宽和能效有极端需求的场景中寻求突破。

从可插拔到共封装,光电器件的集成之路是一条沿着“更近、更密、更高效”方向不断前进的轨迹。这不仅是封装形式的改变,更是光与电在微纳尺度上从“互连”走向“融合”的范式转移。随着硅光技术、先进封装技术和新型材料的持续进步,光电共封装有望在未来十年内,从特定应用逐步走向更广泛的主流市场,成为支撑算力时代指数级增长的关键基石。